If you find any mistake or would like to see any more examples please let me know. Note : Added arbiter model code. Need to add more examples in PLI section . Başka bir görseli rapor et Lütfen rahatsız edici görseli rapor edin.

It is always a good idea if waveform is drawn at various interfaces.

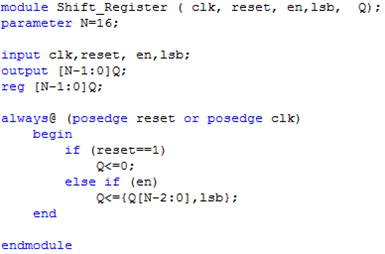

This is phase, where one spends lot of time. Figure : Sample Low level design. Normally we use vim editor, but I prefer conTEXT . Gcc MIPS cross compiler and converting it to ASCII hex . Now we are going to look at the principles of RTL coding for synthesis tools.

Most commercially available synthesis tools expect to be given a design description in RTL form. RTL is an acronym for register transfer level.

It covers modelling clocks, state machines, pipelines, 0-delay code , and race conditions, as well as efficient coding techniques. It is simulator- independent as much as possible, as it covers broadly applicable debugging methods. The synthesis for the examples are listed on page 881.

If you can express working of a digital circuit and visualize the flow of data inside a IC, then learning any HDL or Hardware Description Language is very easy. This article will always be under construction. Let us start with an AND gate.

Here is the truth table: . This page of verilog sourcecode covers HDL code for half adder,half substractor, full substractor using verilog. This page of verilog sourcecode covers HDL code for bit comparator and bit comparator using verilog. HDL Code items naming convention. Verilog Code of Design Examples.

Document abbreviations and additional naming conventions. Global text macros include module name. Instance naming conventions. Signal naming convention – suffixes.

My aim is to display in three consecutive clock cycle.

I studied that for loop will execute sequentially only. But I am not getting output sequentially.