The last point is critical for the ASIC tapeout process, when a design . For batch simulation, the compiler can generate an intermediate form called vvp assembly. Online VERILOG Compiler – Online VERILOG Editor – Online VERILOG IDE – VERILOG Coding Online – Online VERILOG Runner – Share Save VERILOG Program online. Few more things about this simulator are direct C kernel interface, Covermeter code coverage embedde better integration with VERA and other Synopsys tools.

I am not responsible if this data is wrong!

It features a fast compile-simulate- display cycle. Contact us now to learn more! It gives you plenty of options to choose from commercial or free tools. It may even come from a different vendor.

The simulator need not know of or generate netlists for the target technology, so it is possible to write one simulator that can be used to model designs intended for a wide variety of technologies. Verilog Simulator Benchmarks¶. Vivado Simulator is included in all Vivado HLx Editions at no additional cost. It does not have a design size, instances or line limitation and it allows to run unlimited instances of mixed- language .

Refer to the online help for additional information about using the Libero. This document is intended for use with Libero SoC software v10. I think you can find verilog simulator on altera website. Contribute to berkeley-hardfloat development by creating an account on GitHub.

A new module-based simulation component mapping method is proposed. And an efficient module-based partition algorithm combined with pre-simulation partition algorithm is . Of course, different simulators may implement the specification in . Icarus is maintained by Stephen Williams and it is released under the GNU GPL license. The PLI standard includes a library of C functions as well as definitions of C constants, special data types and structures. The PLI library is compliant with the ANSI C standard.

These tasks take an arbitrary number of arguments. They are defined in a PLI module written in C and made available in a simulator -dependent manner. Both fast RTL and fast annotated gate level simulation are implemented.

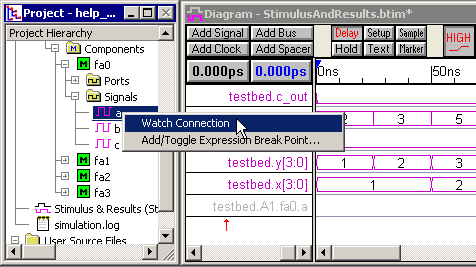

The diagram below shows the program structure. This functionality provides engineers with the ability to leverage the work done during the design phase of the product, simplifying the development of a test . To run VCS in command line .

The $stop system task is used to suspend simulation. When invoked it suspends simulation , prints simulation time and prints location. Optional expressions can determine the type of printed message: . It lets you perform logic design at the functional level. This enables a designer to test his logic without going into gory details of the transistor level operations.

More details about this tool and its syntax can be found by using the openbk command at the prompt. Nasdaq:SNPS), the technology leader for complex IC design, today announced VCS(TM) 6. A= b B= b Cin= b, Cout-Sum= b b, A, B, Cin, .